本实验是同济大学计算机系《计算机系统结构》专业课的课程设计,16级计科学生作品,成功申优免考。 目前,大多数计算机都采用的Cache(高速缓冲存储器)、主存储器和‘’磁盘存储器(辅存)构成的三级存储系统,这个...

”编号:100013267 Verilog 存储系统 课程设计“ 的搜索结果

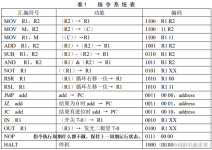

程序和数据统一存储,指令和数据需要从同一存储空间存取,经由同一总线传输,无法重叠执行。根据冯诺依曼体系,CPU的工作分为以下 5 个阶段:取指令阶段、指令译码阶段、执行指令阶段、访存取数和结果写回。

当前,使用免费工具(例如 , 或在FPGA器件中实现数字设计既容易又负担得起如何开始要学习此课程,只需克隆或下载并解压缩该存储库,然后访问其中包含的verilog文件夹。 该文件夹内是每个单元和课程的编号文件夹。 ...

多周期CPU设计报告 文章目录多周期CPU设计报告一、设计思路**1.主要参照:****2.多周期处理器**:**3.指令周期:****4.MIPS指令:**二、主要模块设计**1.总体模块构成****2. MultiCycleCPU.v****3. PCctr.v**3. ...

随着集成电路技术的发展,电子设计自动化(EDA)逐渐成为重要的设计手段...EDA的一个重要特征就是使用硬件描述语言(HDL)来完成的设计文件,Verilog语言是经IEEE确认的标准硬件语言,在电子设计领域受到了广泛的接受。

此课程设计作品是一个可编程电子音乐自动演奏电路,可以通过开关选择预先设定好的音乐曲目并在选定曲目后自动演奏所选曲目。电路内包含了三首长度为1分04秒的乐曲,乐曲根据电子播放器的特点进行了适应性的改编从而...

基于FPGA的出租车计费器的设计

标签: fpga

FPGA课程训练作业

# 1. 引言 ...本文的目的是通过对单总线MIPS CPU的设计与实现,加深对CPU底层原理的理解,掌握CPU的数据通路设计和时序控制器设计的基本原理,进而理解和实现一个较为简单但完整的CPU系统。 ## 1.

接受日期:2016年4月17日2016年8月3日在线发布摘要在这项研究工作中,智能教学系统(ITS)提出了模拟的教育过程中的行为。任何智能教学系统都包括一个教学模块、一个问题选择器、一个专家模块、一个学生模型和一个...

关于单周期CPU的设计问题,相信各位在课程上也有所学习,以下是个人的一些理解 整个项目的资源下载:这里写链接内容 实验内容 基本要求 PC和寄存器组写状态使用时钟触发,这是必须的! 指令存储器和数据...

芯片原厂必学课程 - 第六篇章 - FPGA 设计篇

-数字逻辑与数字系统设计-章节资料考试资料-中国矿业大学【】 第 1 讲 绪论-单元作业 第 1 讲 绪论-单元测试 1、【单选题】现代电子技术的发展,目前集成电路器件处于()阶段。 A、分立元器件 B、集成电路 C、大...

本文大部分内容来自Clifford E. Cummings的《Simulation and Synthesis Techniques for Asynchronous FIFO Design》,经过自己的一些改变,理论部分为转载,代码自己完成。 一、FIFO简介 FIFO是英文First In ...

推荐文章

- Unity3D 导入资源_unity怎么导入压缩包-程序员宅基地

- jqgrid 服务器端验证,javascript – jqgrid服务器端错误消息/验证处理-程序员宅基地

- 白山头讲PV: 用calibre进行layout之间的比对-程序员宅基地

- java exit方法_Java:如何测试调用System.exit()的方法?-程序员宅基地

- 如何在金山云上部署高可用Oracle数据库服务_rman target sys/holyp#ssw0rd2024@gdcamspri auxilia-程序员宅基地

- Spring整合Activemq-程序员宅基地

- 语义分割入门的总结-程序员宅基地

- SpringBoot实践(三十五):JVM信息分析_怎样查看springboot项目的jvm状态-程序员宅基地

- 基于springboot+vue的戒毒所人员管理系统 毕业设计-附源码251514_戒毒所管理系统-程序员宅基地

- 【LeetCode】面试题57 - II. 和为s的连续正数序列_leet code 和为s的正数序列 java-程序员宅基地